66AK2L06, TCI6630K2L SoC는 풍부한 하드웨어 및 소프트웨어 개발 환경을 제공하며, 고속 데이터 컨버터와 원활하게 연결해 준다. 여기서는 66AK2L06 SoC가 임의 신호 제너레이터와 실시간 스펙트럼분석기(SA, Spectrum Analyzers)에서 어떤 장점을 발휘하는지 알아보고, 이동통신 테스트 제품을 위한 비용 효과적인 솔루션, TCI6630K2L SoC에 대해서도 살펴본다.

사람과 기계, 기계와 기계를 연결해 상호 작용하게 하는 방식들이 새로 등장하면서 테스트&측정(T&M: Test and Measurement) 시장에서 새로운 문제들이 부각되기 시작했다. 제품 개발과 제품 제조 기간은 물론, 제품 수명시간 내내 테스트와 검증을 효과적으로 하기 위해 미래에도 사용할 수 있는 비용 효율적인 새로운 T&M 제품들이 필요해진 것이다.

T&M 시장은 세부적으로 3개 분야로 나눌 수 있고, 각 분야마다 고유의 특성을 갖고 있다. 첫 번째 분야는 다목적 T&M 분야다. 여기에는 오실로스코프와 신호나 로직 분석기/제너레이터 같은 엔드 애플리케이션(End Applications)이 포함된다. 이러한 종류의 장비는 실험실부터 제조 테스트, 현장 테스트에 이르기까지 다양한 산업에서 사용된다. 또 다른 분야는 기계 테스트 분야다 여기에는 비파괴 테스팅(NDT: Non-Destructive Testing), 산업 엑스레이, 재료 테스팅, LIDAR와 같은 고정밀 치수 측정 등이 포함된다. 마지막 세 번째 분야는 유선, 무선, 광학, 이동통신 등의 시장을 위한 제품으로 이동통신 테스트를 실시하는 것이다.

이 세 분야의 요건들은 TI의 새로운 시스템온칩(SoC) 66AK2L06과 TCI6630K2L의 프로세싱 성능 및 가속 기능을 이용해 충족시킬 수 있다. 두 SoC 모두 풍부한 하드웨어 환경과 소프트웨어 개발 환경을 제공한다. 이러한 환경은 개별 ADC(Analog-to-Digital Converters)와 DAC(Digital-to-Analog Converters)부터 GUI(Graphical User Interface) 연결 및 외부 대량 저장에 이르기까지 모든 단계에서 신호를 생성, 처리, 분석하는 데 필요한 기능들을 통합하고 있다.

이 SoC들은 DFE(Digital Front End)와 JESD204B 인터페이스가 고도로 집적된 솔루션을 제공함으로써 ADC, DAC, AFE(Analog Front Ends) 등의 고속 데이터 컨버터와 매끄럽게 연결될 수 있도록 한다. 여기서는 다목적 테스터 분야에서 사용되는 66AK2L06 SoC의 기능과 장점에 대해 자세히 살펴본다. 그리고 이동통신 테스트 제품을 위한 TCI6630K2L SoC에 대해서도 알아본다.

애플리케이션 개요

신호 제너레이터는 T&M 시장에서 핵심 툴이라고 할 수 있다. 이것은 윤곽이 뚜렷한 신호를 만들어 내 엔지니어가 장치를 탐색, 테스트할 수 있게 해준다. 초기 장비들은 단순한 연속 파형을 생성했지만, 신호 처리 산업이 빠르게 발전하면서 테스트 신호가 더욱 복잡해졌고 신호 제너레이터에 대한 제어 요구도 이에 맞춰 늘어났다.

현대의 신호 제너레이터는 예상되는 변조 파형을 생성할 수 있어야 하고, 아울러 현장 테스트 상황에서 신호에 영향을 줄 수 있는 간섭과 감손도 모방할 수 있어야 한다. 이러한 신호 제너레이터는 현재 산업 전반에 널리 이용되고 있다.

이와 같은 측면에서 가장 까다로운 산업이 무선통신과 항공, 위성, 국방 등이다. 이들은 벡터 신호 제너레이터(VSG: Vector Signal Generators)를 필요로 하는데, VSG는 미리 규정된 형식에 맞춰 디지털 방식으로 변조된 신호를 만들어 낸다. 측정 유형에 따라, 생성된 신호는 사용자 장비를 테스트하기 위한 정보를 담고 있을 수도 있다.

가장 흔한 벡터 측정이 ACPR(Adjacent Channel Power Ratio)과 같은 전력 측정과 EVM(Error Vector Magnitude)과 같은 감도 및 선택도, 진폭/위상 오류다. 측정 정밀도는 VSG의 정밀도에 좌우된다. 예시는 다음과 같다.

• 전력 레벨 정밀도는 장비 감도 측정에 영향을 미친다.

• 진폭/위상 레벨의 정밀도는 장비 신호 왜곡 측정에 영향을 미친다.

• 주파수 레벨 정밀도는 장비 선택도 측정에 영향을 미친다.

어떤 테스트 애플리케이션들은 VSG가 매우 깨끗한 신호를 만들어 내도록 요구하기도 한다. 이것은 신호 제너레이터가 신호에 오류를 넣을 수 있으므로 어려울 수 있다. 그러나 무선 통신 분야에서 입증된 전치 왜곡(Predistortion) 기법을 사용하면 이러한 감손을 보정할 수 있다.

T&M 시장의 신호 제너레이터와 본질적으로 짝을 이루는 것이 SA이다. 오늘날의 SA는 주파수 도메인에 신호의 스냅 샷을 제공하는 저렴한 스웹트-튠드(Swept-turned) SA부터, 위상 정보를 추가해 디지털 변조를 분석할 수 있게 해 주는 벡터 SA, 스펙트럼 분석 안에 시간 도메인을 제공하는 실시간 SA까지 다양하다. 최근 SA가 다루어야 할 고급 측정 과제들은 다음과 같다.

• 트랜션트 다이내믹 신호 캡처 및 분석 스프레드 스펙트럼 및 주파수 홉핑 신호

• 버스트 전송, 글리치, 스위칭 트랜션트

• 주파수 드리프팅

• 노이즈 분석

• 변조 품질 진단을 비롯한 변조 분석

테스트할 장비가 이미 현장에 배치돼 있는 경우, 포터블 테스트 장비가 필요하다. 최근 트랜시버 장비가 증가함에 따라 무선 네트워크 성능을 최적화하기 위한 유지관리 및 테스트에 대한 필요성도 빠르게 증가하고 있다. 컴플라이언스 테스트나 현장 테스트용 생산 테스트에 사용되는 것과 같은 고정밀 실험실 장비는 사용할 수 없다. 현장 내 테스트에서는 탄력적이면서도 휴대하기 편하고 상대적으로 값이 저렴한 테스트 장비가 필요하다. 더 나아가 자체 캘리브레이션이나 자동 진단을 위한 T&M 기능을 그 장비에 넣을 수도 있다.

휴대하기 편리한 임베디드 테스트 장비는 감소된 C-SWaP(Cost, Size, Weight, Power)로 탄력성과 정밀성의 균형을 이루어야 한다. C-SWaP는 일부 지역에서 SWaP-C(Size, Weight, Power, Cost)라고 부르기도 한다.

TI의 KeyStoneTM SoC 기반 멀티코어 디바이스는 비용효과적인 성능과 저전력 소비로 C-SWaP 효율의 핵심이라고 할 수 있다.

■ 66AK2L06의 주요 기능

• 2개의 ARM Cortex-A15 RISC 코어 @ 1.2GHz와 8400DMIPS

• 4개의 TMS320C66x DSP 코어 @ 1.2GHz와 고정 및 부동소수점 프로세싱으로 76GFLOPS, 153GMACS 제공

• 통합 DFE 기술과 프로그래머블 필터링, IQ 불균형 교정, 업 앤 다운 샘플링 등으로 과중한 신호 처리의 부담을 없앰

• 고급 통합 네트워크 코프로세스로 ARM 및 DSP 코어에서 IP 라우팅과 IP 터미네이션의 부담을 없앰

• 2개의 FFTC(Fast Fourier Transform Coprocessor)로 최대 8K-포인트까지 FFT/인버스 FFT(iFFT) 실행을 위한 레이턴시 개선, 고정 소수점 DSP 코어 구현보다 성능 개선

• 코어 및 액셀러레이터와 2MBytes 메모리를 공유하는 MSMC(Multicore Shared Memory Controller)

• 멀티코어 네비게이터가 멀티코어 SoC 소프트웨어 디자인에 싱글코어 단순 동작 제공

• 이더넷 스위치와 4×1GbE 포트

• 2개 싱글레인 PCIe Gen2 인터페이스로 최대 5GBaud 지원

• 고속 JESD204B 칩-투-칩 인터페이스로 최대 4개 레인을 각각 7.37Gbps씩 지원

• 콤팩트한 패키지 사이즈(25mm×25mm FPBGA)

새로운 TI 66AK2L06 SoC는 T&M 장비 설계자에게 혁신적인 성능과 SWaP-C 효율을 제공한다. TI의 새로운 KeyStone Ⅱ 멀티코어 아키텍처에 기반을 둔 66AK2L06 SoC는 TI 고정 및 부동소수점 TMS320C66x DSP(Digital Signal Processors), ARM? Cortex?-A15 ZHDJ, 고급 신호 처리 액셀러레이터 등의 프로세싱 구성 요소들을 통합하고 있다.

66AK2L06 SoC에는 고속 JESD204B 인터페이스가 탑재돼 있어 TI의 고속 ADC, DAC, AFE와 바로 연결 가능하다. 소프트웨어 프로그래머블 DFE의 통합으로 가능해진 디지털 변환 및 디지털 필터링 덕분에 일련의 개별 컴포넌트들이 필요 없어지고, 전력 및 보드공간이 줄어들어 작은 풋프린트에서도 최고의 와트당 전력을 생산해 낼 수 있다.

디바이스

점점 정교해지는 신호 처리 알고리즘에 맞춰 항공, 레이더, 초음파, T&M, 무선통신 같은 파형 집약적 애플리케이션들을 선도하는 핵심 기술은 멀티코어 DSP 코어를 사용하는 것이다. 멀티코어 기능과 AccelerationPac의 확장 어레이, 통합 트랜스포트 솔루션을 조합하면 작은 폼팩터에서도 놀라운 전력 소비로 높은 성능을 발휘할 수 있다. 지원되는 애플리케이션과 사용되는 인터페이스에 따라, 66AK2L06 SoC의 전력소비 범위는 100℃(케이스 온도)에서 6W부터 12W까지 다양하다.

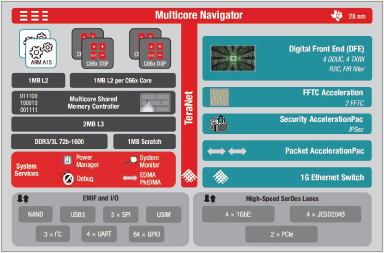

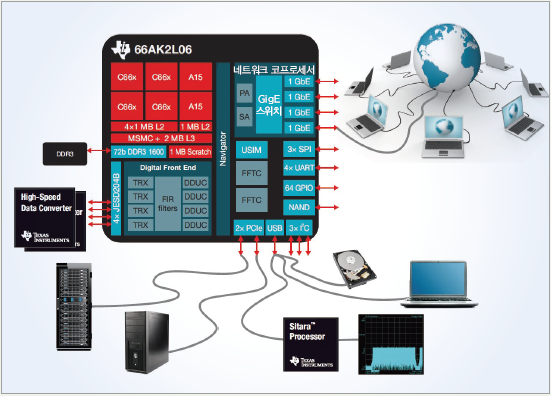

KeyStone Ⅱ 플랫폼의 주요 목표는 접속성, 여분의 처리 능력, 온칩 리소스를 제공해 프로세싱 코어가 아무 제약 없이 최적의 프로세싱 성능을 달성할 수 있도록 하는 데 있다.[3] ‘Multicore Entitlement’라고도 불리는 프로세싱 코어의 권한 부여는, 모든 프로세싱 코어, 주변장치, 코프로세서, I/O 채널에 차단 없이 액세스를 제공하는 이 아키텍처의 능력을 통해 달성된다. KeyStone Ⅱ 아키텍처의 핵심 요소들(그림 1)은 Multicore Navigator, TeraNet, Multicore Shared Memory Controller이며, 이것은 다시 JESD204B 부수 애플리케이션들을 위한 탄력적이고 확장성 높은 솔루션을 낳게 된다.

▲ 그림 1. 66AK2L06 SoC 블록 다이어그램

TI는 JESD204B 인터페이스에서 ADC와 DAC의 시스템 요건들을 충족시키기 위해 점점 더 많은 옵션들을 제공함으로써 66AK2L06 SoC와 직접 연결할 수 있게 했다. JESD204B 인터페이스에서의 ADC는 50Msps부터 4Gsps까지의 샘플 레이트와 12비트부터 16비트까지의 해상도를 제공한다. 더 높은 샘플링 레이트를 가진 디바이스에는 종종 샘플 레이트를 떨어뜨릴 수 있는 구성형 우회 데시메이션이 포함되기도 한다.

JESD204B 인터페이스에서의 DAC는 듀얼 채널 디바이스부터 쿼드채널 디바이스까지 다양하다. 이 샘플 레이트는 1.6∼2.8Gsps, 디지털 기능은 인터폴레이션, NCO(Numerically Controlled Oscillators), 믹서 및 게인 등 다양하며 주파수 배치를 최적화하고 데이터 입력 레이트를 최소화할 수 있다. TI는 올해 새로운 제품군들로 RF 샘플링 ADC 및 DAC의 토대를 쌓을 예정이다.

임의 신호 제너레이터

66AK2L06 SoC는 신호 제너레이터를 임베디드 하드웨어 장치나 독립형 장치로 구현하는 데 잘 맞는다. 이것은 최대 4개까지 사용자 정의 파형(DSP와 Keystone 액셀러레이터를 이용해 합성)이나 외부 대량 저장장치에서 가져온 테스트 패턴을 최대 집계 대역폭(BM) 660MHz와 달성 가능한 점유 대역폭(OBW) 350MHz에서 동시에 만들어 낼 수 있다. 만들어진 신호는 외부 트리거나 내부 트리거를 이용해 반복될 수도 있으며 일회성일 수도 있다. 이 디바이스는 변조된 테스트 벡터(QAM, QPSK, FSK, BPSK, OFDM)를 생성해 상업용 및 군사용 무선 통신 장비를 테스트하는 데 사용할 수도 있다.

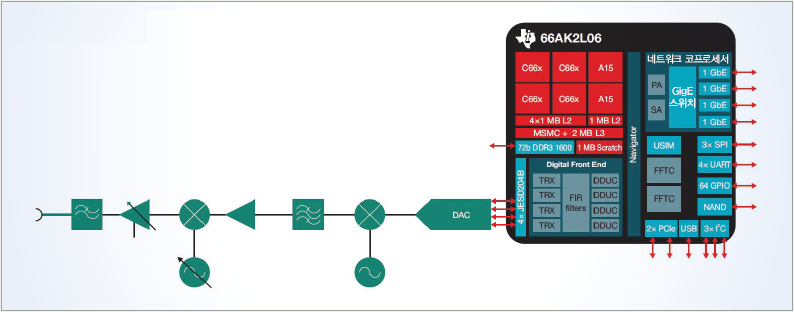

그림 2는 66AK2L06 SoC(임의 파형 제너레이터)와 아날로그 업-컨버터를 함께 사용하는 신호 제너레이터의 구현 모습이다. 66AK2L06 SoC는 다음과 같은 동작을 수행한다.

▲ 그림 2. 임의 신호 제너레이터 다이어그램

• 파형 합성 : 외부나 내부 메모리에 저장된 테스트 벡터 또는 기지의 패턴을 바탕으로, DSP는 일련의 온-더-플라이 베이스밴드 복잡 신호들을 만들어 낼 수 있다.

• 스트리밍 : 베이스밴드 복잡 샘플들은 내부 메모리에서 가져와 그 베이스밴드 레이트의 프로그래머블 필터에 제출된다. 스트리밍은 연속적일 수 있고 트리거에 의해 시작 및 중단될 수도 있다. 저주파수 신호의 경우, 소프트웨어에서 인터폴레이션을 수행한 후에야 디지털 파형을 스트리밍할 수 있다.

• 게인 조정 : DFE 데이터 경로 사용을 최대화할 수 있게 샘플 진폭이 조정된다.

• 필터링: DFE에는 네 개의 프로그래머블 FIR 필터 뱅크와 패로우 리샘플링 필터, CIC (Cascaded-Integrator-Comb) 필터가 있다.

• 믹싱 : NCO는 다음 정밀도로 베이스밴드 파형의 캐리어 주파수를 조정한다.

• 결합 : 여러 파형의 BW에 따라, DFE는 최대 12개를 같은 출력 스트림에서 결합시킬 수 있다. DFE는 네 개의 컴포짓 스트림을 만들 수 있다.

• 선택적 아날로그 감손 보정 : 예컨대 IQ 왜곡 보정

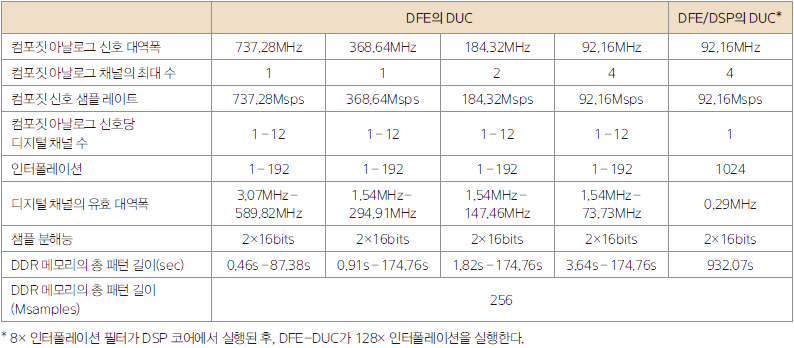

디지털/아날로그 업-컨버터 체인에는 일단의 DAC가 들어 있는데, 여기에는 인터폴레이션 필터, 일부 아날로그 믹서, 필터 및 진폭기 등이 들어 있을 수 있다. 텍사스 인스트루먼트의 다양한 DAC와 AFE는 JES204B 서브클래스 0과 1을 지원한다. 이들을 66AK2L06 SoC와 연결하여, 넓은 스펙트럼 범위의 신호 생성이나 좁은 스펙트럼 범위의 신호 생성을 지원할 수 있다. 표 1은 66AK2L06 SoC가 지원할 수 있는 합성 구성들의 몇 가지 예를 든 것이다. 이 디바이스의 저장 능력은 크기와 처리량에 있어서 긴 멀티채널 파형 패턴도 생성할 수 있도록 해 준다는 데 주목해야 한다. 66AK2L06 SoC DDR 인터페이스의 이러한 성능은 가장 높은 신호 BW에서도 실시간 패턴을 사용할 수 있게 한다.

▲ 표 1. 신호 제너레이터 사용 예제

1. 파형 합성

임의 파형 또는 테스트 벡터는 66AK2L06 및 TCI6630K2L SoC에서 손쉽게 생성할 수 있다. 두 SoC를 위해 최적화된 신호 처리 라이브러리와 TCI6630K2L SoC를 위한 무선 통신 액셀러레이터를 사용하면 된다.

DSPLib은 16b와 32b 신호에 최적화된 보정과 컨볼루션, 필터링, 벡터 등을 동작시킨다. 예를 들어, 복잡 벡터(1×1024)에 FIR 필터를 적용하면 샘플당 탭당 약 1.13 사이클이 걸린다(예를 들면, 싱글 1.2GHz DSP 코어에서 16-탭 필터의 경우 15.4마이크로초). 복수의 파형들이 동일한 컴포짓 신호에 결합돼 있는 경우, 동일 밴드 샘플링 레이트를 사용해 그 파형들과 연관된 디지털 채널들을 형성해야 한다.

2. 스트리밍

복수의 디지털 채널과 관련된 패킷 베이스밴드 샘플들은 DFE 베이스밴드 인터페이스가 내부 메모리(MSMC)나 외부 메모리(DDR)에서 가져온 후 필터 뱅크로 스트리밍한다. 66AK2L06 SoC는 최대 32개의 디지털 채널들을 동시에 스트리밍할 수 있다.

3. 게인, 혼합, 결합

구성에 따라, 각 DUC 필터 블록은 최대 12개 디지털 채널을 동시 처리할 수 있다. DFE의 DDUC 블록은 다음을 지원한다.

• 디지털 채널의 게인, 위상, 딜레이 조정(필터링 전 또는 후).

• 디지털 채널의 인터폴레이션. 인터폴레이션은 애플리케이션이 요구하는 주파수 범위에 샘플링 레이트를 맞추는 데 사용된다. 프로그래머블 필터링은 합성된 신호의 스펙트럼 방출 요건을 충족시키는 데 사용된다.

• 디지털 채널의 업 변환. NCO 주파수는 고정이거나, RFSDK (Radio Frequency Software Developer Kit)를 통한 DSP 제어로 변동한다. 후자의 옵션을 통해 스웹트 신호(Swept Signals) 합성이 가능해진다(660MHz 범위 내에서).

전력 계량기를 사용해 디지털 채널 각각의 전력을 각각 따로 감시할 수 있다. 업 변환된 디지털 채널들을 같은 컴포짓 신호에서 선택적으로 누적시킨다. DFE는 4개의 별도 컴포짓 신호들을 만들 수 있다. 컴포짓 신호의 주파수 범위는 JESD204B 인터페이스에 할당된 BW에 의해 제한을 받는다. 이와 관련된 예는 표 1에 설명돼 있다.

4. 감손 보정

아날로그 컴포넌트들은 IQ 불균형과 비선형 왜곡 같은 감소에 시달린다. 예를 들어, 아날로그 쿼드러처 모듈레이터는 자기의 세 개 지류에서 동일한 진폭을 가질 수 없고, 전체 신호 대역에서 90° 위상 시프터를 온전하게 할 수도 없다. 이것은 테스트 환경에서 측정 품질에 나쁜 영향을 줄 수 있다. 측정 장비는 트랜스미터 장비에 감손이 없을 것이라고 가정하는 경우가 일반적이기 때문이다. 측정 장비에서 어떤 감손은 보정이 가능하지만, 또 다른 전략은 제너레이터에서 이를 보정하는 것이다.

66AK2L06 SoC에는 백-엔드 자동 게인 컨트롤이 있다. 이것은 데이터 컨버터의 범위 사용을 최적화하는 데 도움이 되고, 인-채널 성능을 최적화하거나(따라서 EVM 감소) 대역 밖 성능을 최적화하는 데(따라서 ACPR 감소) 쓸 수 있는 프로그래머블 FIR 필터의 사용을 최적화하는 데에도 도움이 된다.

RFSDK 소프트웨어는 LTE와 CDMA 성능을 위해 EVM/ACPR 조정을 최적화시킨 사전 필터들을 제공하고 있다. 또한 이를 통해 사용자는 자신만의 필터를 규정할 수도 있다.

신호 합성(TX 경로)과 신호 측정(피드백 경로)을 동시에 처리할 수 있는 66AK2L06 또는 TCI6630K2L SoC의 기능을 이용하면 더 진화된 보정을 구현할 수 있다. 이렇게 합성된 신호는 DSP 코어에서 실행된 실시간 적응 (블라인드 또는 캘리브레이션) 알고리즘을 바탕으로 감손에 대해 사전 보정된다. TCI6630K2L SoC는 이때 필요한 피드백 경로를 가능케 한다.

5. 66AK2L06 SoC에서 전력 예측

66AK2L06 SoC는 합성되거나 수신된 신호의 전력을 여러 가지 방식으로 감시할 수 있다. DFE에는 16개의 탄력적인 전력 계랑기가 들어 있는데, 이것을 여러 처리 단계에서 스트리밍 신호의 전력을 측정하도록 구성할 수 있다.

신호 합성기의 경우 DFE는 게인, 필터링, 인터폴레이션 전후로 디지털 채널 컴포넌트(최대 16비트 범위)의 전력을 감시할 수 있다. 또한 필터링 전후로 디지털 채널의 선택적 결합 후 디지털 컴포짓 신호의 전력을 감시할 수도 있다.

SA의 경우, DFE는 수신된 신호의 전력(최대 24비트 범위)과 게인, 필터링, 데시메이션 후 서브채널의 전력을 감시할 수 있다. 전력 계랑기는 트리거 시 작동하는 일회성 모드로 사용할 수 있고, 구성형 RMS/평균 체계와 최소 및 최대 기록을 실행하는 연속 모드로 사용할 수도 있다.

RFSDK의 소프트웨어 API는 전략 계량기를 설정하고, 다른 API는 전력 계량기 값을 읽는다. 연속 모드에서 측정 시퀀스 제어는 타이머와 카운터를 통해 자동으로 이루어진다. 전력 계량기에 워터마크를 사용하여 추가 처리를 촉발하게 할 수도 있다. 예를 들어, 트랜션트 신호를 수신했을 때 고급 스펙트럼 분석이 촉발될 수 있다. DSPLib 역시 실제 신호나 복잡 신호에서 작동하는 C66x 최적화 기능들을 여러 가지 제공함으로써 보다 진화된 전력 분석을 지원하고 있다.

임의 스펙트럼 분석기

66AK2L06 SoC는 스펙트럼 분석기 기능을 구현하는 데 적합하다. 이것은 JESD204B 인터페이스 덕분에 소형 저전력 구현이 가능하다. JESD204B 인터페이스는 ADC와 직렬화된 직접 연결을 가능하게 해주고 충분한 처리 자원, 필터링 자원, FFT 자원으로 가장 흔한 세 개의 스펙트럼 분석기, 스웹트 튜너블(Swept Tunable) SA, 벡터 SA, 실시간 SA를 구현할 수 있게 해 준다.

스웹트 튜너블 SA는 수십 년간 사용돼 온 전통적인 SA 아키텍처이다. 스웹트 튜너블 SA는 원래 아날로그 컴포넌트로만 구현됐지만, 지금은 ADC와 일부 디지털 신호 프로세싱도 포함돼 있다. 이것은 신호를 다운 변환하여 그것을 리솔루션 BW 필터의 패스밴드를 통해 쓸어버리는 방식으로, 넓은 신호 BW에서 주파수 대 전력 측정을 할 수 있도록 고안된 것이다. 스웹트 튜너블 SA의 장점은 높은 다이내믹 레인지와 함께 그것이 처리할 수 있는 커다란 신호 BW에 있다. 이것이 BW를 통해 스위핑할 수 있다는 것은, 한 번에 한 주파수 포인트에서만 전력 레벨을 계산할 수 있고, 그러면 비교적 안정적인 입력 신호 환경에서 최적으로 작동할 수 있다는 뜻이다.

벡터 SA는 전력 레벨을 측정할 수 있을 뿐 아니라 위상 정보를 추가해 디지털 변조된 신호를 변조 측정할 수도 있다. VSA는 IF 신호를 디지털화하여 디지털 도메인에서 다운 변환, 필터링, 검출을 실행한다. 시간에서 주파수 도메인으로 바뀌는 것은 FFT 프로세싱을 통해 이루어진다.

실시간 SA는 주파수 대비 전력 및 위상 측정을 실행한다. 이것은 시간 도메인 데이터를 표시할 수 있고 매끄럽게 신호를 캡처한다. 이것은 실시간 트리거링 및 시간과 상관된 다차원 측정을 수행할 수 있어 비연속적인 신호 문제들, 예를 들면 글리치, 트랜션트, 버스트 전송, 기타 동적 현상이나 간헐적 현상들을 검출해 낼 수 있다.

여기서는 66AK2L06 SoC가 실시간 SA의 요건을 어떻게 처리할 수 있는지 살펴본다. 이 세 가지 애플리케이션이 디지털 처리 관점에서 가장 까다롭고, 다른 두 개 유형의 기능을 모방할 수 있기 때문이다.

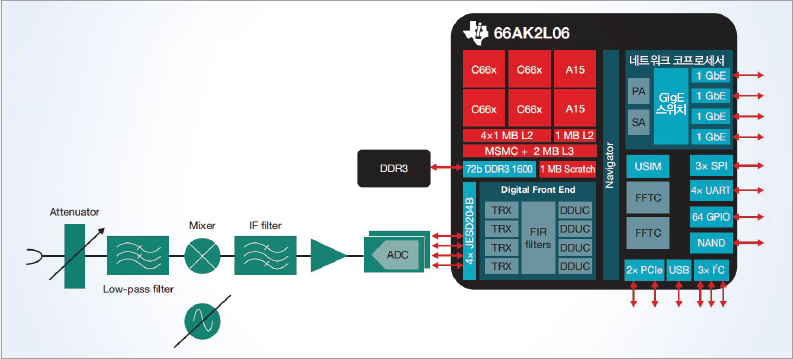

그림 3은 66AK2L06 SoC를 사용하는 실시간 SA의 일반적인 블록 다이어그램이다. RTSA의 AFE를 기기의 전체 주파수 범위에서 튜닝할 수 있고, 이것은 입력 신호를 실시간 SA의 BW와 일치하는 고정 IF 신호로 다운 변환한다. IF 신호는 필터링과 디지털화를 거친 후 JESD204B 인터페이스의 SoC로 전송된다. 그 후 이 신호는 시간 및 주파수 도메인에서 다운 변환되고 처리된 후, 결과를 내놓는다.

▲ 그림 3. 실시간 스펙트럼 분석기의 일반적인 블록 다이어그램

1. 신호 프로세싱

66AK2L06 SoC는 스펙트럼 분석에 사용되고 데이터의 샘플, 프레임, 블록에 적용되는 디지털 신호 처리 기법들을 지원할 수 있다.

① 샘플 레벨 프로세싱

• DFE의 DDUC 액셀러레이터는 캡처된 샘플들의 필터링을 지원한다. 가변 밴드 로우패스 필터링을 사용하여 들어오는 신호의 일부를 거부하거나 이를 형성할 수 있다.

• DFE의 DDUC 블록은 캡처된 샘플의 다운 변환과 데시메이션을 지원한다(I/Q 페어). 데시메이션은 샘플링 레이트를 사용자가 요구하는 주파수 범위에 맞추는 데 사용된다.

② 프레임 레벨 프로세싱

• FFTC 액셀러레이터는 FFT, iFFT, DFT, iDFT를 지원한다.

• DSPLib은 최적화된 다양한 고정 및 부동소수점 FFT와 실시간 데이터 및 복잡 데이터를 위한 DFT C66x 루틴을 제공한다.

③ 블록 레벨 프로세싱

• DSPLib은 매끄러운 스펙트럼 윈도우를 구현할 수 있도록 최적화된 벡터 곱셈 루틴을 제공하고 있다.

• MCSDK(Multi-Core Software Developer Kit)는 중첩되는 스펙트로그램에서 대형 데이터 블록 조정을 지원한다.

• DSPLib은 멀티 도메인 분석에 사용할 수 있도록 다양한 종류의 필터링, 상관관계, 컨볼루션 루틴들을 제공하고 있다.

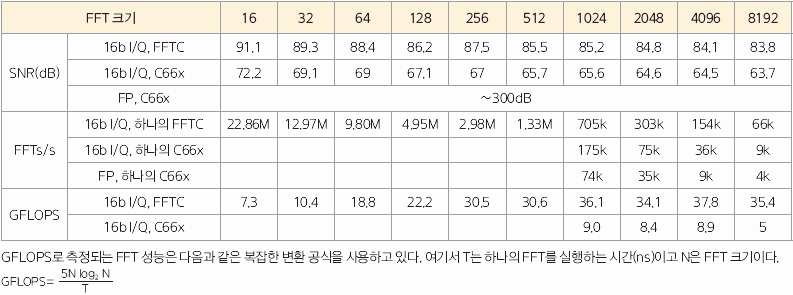

표 2는 Fast Fourier Transform의 구현 방식[FFTC에서의 16b 고정소수점 I/Q, C66x에서의 16b 고정소수점 I/Q, C66x에서의 부동소수점(FP)]에 따라, 66AK2L06 SoC에서 기대되는 성능을 보여준다.

▲ 표 2. FFT 성능 표

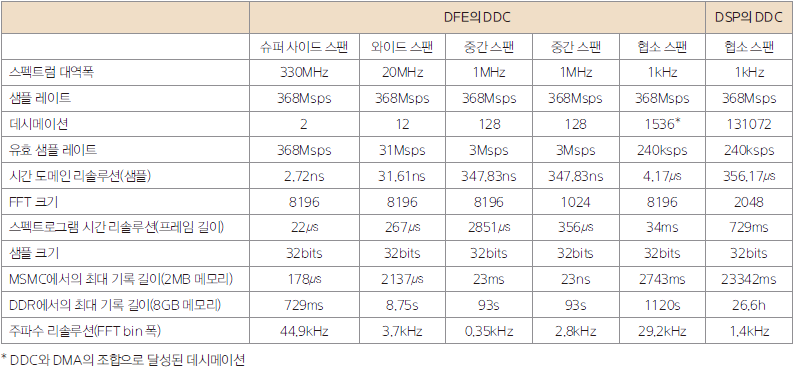

DFE 블록의 DDC와 필터링을 FFTC 및 C66x 코어의 FFT 성능과 함께 활용할 경우, 66AK2L06 SoC는 여러 가지 SA 사용 예제를 지원할 수 있다. DFE 블록의 디지털다운 컨버터는 최대 다운 변환율이 192이다. 더 높은 비율이 필요할 경우, DFE DDC 필터가 총 데시메이션의 나이퀴스트(Nyquist) 한계를 충족시키기만 한다면, 디바이스 DMA 인프라를 이용해 이 DFE 한계를 극복할 수 있다. DFE의 모든 샘플을 FFTC로 넘기는 대신, DMA 엔진은 두 개, 네 개, 여덟 개 샘플들 중 하나를 넘긴다. 이는 최대 데시메이션을 1,536으로 증가시킨다. 추가 데시메이션이 필요할 경우, C66x DSP 코어와 DSPLib의 최적화된 기능들을 이용해 손쉽게 구현할 수 있다. 표 3에 SA 용례가 몇 가지 나와 있다. 극단적인 예로 DSP를 다운 변환에 사용하는 것을 들 수 있다.

▲ 표 3. 스펙트럼 분석기의 신호 채널 사용 예제

표시된 샘플 레이트는 복잡한 데이터를 가정한 것으로, 368Msps는 실제 데이터에서 736Msps에 해당한다. 이것은 현재 66AK2L06 SoC DFE 블록이 지원할 수 있는 상한이며, JESD204B 인터페이스에서 두 개의 레인에 7.3Gbps의 속도가 필요하다. 향후 개량 버전에서는 더 높은 클록 속도에서 DFE를 실행할 것이고, 따라서 샘플링 레이트도 높아질 것이다.

표 3의 예들은 모두 연속 획득을 이용해 FIFO로 구성된 DDR 메모리에 데이터를 저장할 수 있다. 가장 높은 레이트는 DDR BW 능력의 12%를 넘지 않는다. 그러므로 DSP에서 실시간 트리거를 구현할 수 있다. 일단 트리거링이 이루어지면, 데이터 획득이 즉시 중단될 수 있고, 지정 시간 동안 계속 실행되게 하여 트리거 포인트 전후의 분석에 쓸 데이터를 충분히 저장할 수도 있다.

FFT 프레임들 사이의 단절로 인한 스펙트럼 누손을 피하기 위해, FFT 프레임 윈도잉과 오버랩핑을 함께 적용할 수 있다. 윈도잉은 FFT 프레임의 엣지에 가깝게 샘플들을 약화시킨다. 이때 윈도잉으로 인해 프레임 에지에 가까운 스펙트럼 이벤트를 잃지 않게끔 오버래핑 FFT 프레임이 힘을 쓰는 동안 인위적인 가짜 응답이 일어날 것이다. DSP 코어와 최적화된 라이브러리 기능들을 사용해 FFTC의 결과를 사후 처리함으로써 윈도잉을 구현할 수 있다. 두 개의 FFTC 액셀러레이터는 오버래핑 FFT 프레임을 비롯한 모든 FFT 프로세싱의 부담을 완전히 제거할 수 있으며, 더 진화된 신호 처리 작업을 위해 이 DSP 자원을 보전할 수 있다. 패킷 DMA 엔진은 프로세서 개입 없이도 메모리 매핑 위치들 간에 서로 데이터를 이동시킴으로써 극단적인 데이터 관리 문제를 해결한다. 모든 데이터 블록과 관련해, 디스크립터가 그 이동의 출처와 목적지 주소를 알려주고 그 데이터의 구조도 알려 준다. 이 디스크립터는 프로세싱 코어나 주변장치를 통해 생성된다. 하드웨어 대기열에 분배되며 멀티코어 네비게이터의 관리를 받는다.

DFE 블록의 짐을 덜어 줄 수 있는 또 다른 기능이 IQ 불균형 보정이다. 이것은 JESD204B 리시버 블록 내의 로직을 이용해 구현된다. 상관관계 파라미터는 JESD204B 블록의 복잡한 게인 불균형 보정 정보를 바탕으로 예측하거나, 싱글-탭 블라인드 예측 알고리즘을 바탕으로 예측된다. 이 기능은 제로 IF 복잡 스트림이 RX 서브-블록에 입력될 때 유용하다.

2. 트리거

66AK2L06 SoC는 여러 종류의 탄력적인 트리거를 구현할 수 있게 해 준다. 이 트리거를 이용해 데이터를 획득하거나 중단할 수 있다. 그리고 이것은 크게 두 개의 카테고리로 나뉜다.

① 외부 트리거는 64 GPIO 중 하나에서의 변화를 통해 또는 PCIe, 이더넷, I2C, SPI, UART, USB, JESD204B 등의 복잡 I/O 중 하나를 거친 메시징을 통해 트리거링할 수 있다.

② 내부 트리거는 코어나 신호 처리 액셀러레이터를 통해 생성된다. 내부 트리거에서 가장 흥미로운 것 중 하나가 DFE에 의해 생성된다. ADC의 데이터를 처리하는 동안, 이것은 들어오는 데이터의 특성을 기반으로 트리거를 생성할 수 있다. 내부 트리거의 예제는 다음과 같다.

• 전력 기반 DFE 트리거: 이것은 필터링과 데시메이션이 전체 스펙트럼을 바라보기 전에 ADC 디지털 신호의 전력 레벨을 바탕으로 할 수 있고, 필터링과 데시메이션 후의 전력 레벨을 바탕으로 할 수도 있다. DFE 블록에는 여러 가지 빌트인 전력 계량기가 있어서 DDC와 필터링 전후로 전력을 측정할 수 있다.

• 소프트웨어 기반 주파수 트리거: 주파수 기반 트리거는 C66x DSP를 이용해 소프트웨어에서 구현할 수 있으며, 따라서 매우 탄력적이다. DSP는 FFTC의 모든 결과를 사후 처리할 수 있으므로 선택된 스펙트럼 부분에서 규정 역치를 위로 벗어나거나 아래로 벗어나는 특정 전력 레벨에 대해 복잡한 주파수 마스크들이 트리거링하게 할 수 있다. 실시간 분석을 가능하게 하기 위해 패킷 DMA 엔진이 DSP 코어와 FFTC 간의 모든 내부 DAM 트래픽에 사용되므로 DSP의 부담이 제거된다.

트리거 분석이 실시간으로 실행되면, 소프트웨어 정의 타이머를 이용해 트리거 포인트 전후로 DDR에 얼마나 많은 데이터를 저장할지 세부적으로 활용할 수 있다. 이를 통해 사용자는 트리거가 발생하기 전과 후 모두 스펙트럼 분석을 시행할 수 있게 된다.

I/O 연결

실리콘 레벨에서 통합성이 커지는 것 외에도, 66AK2L06 SoC는 JESD204B, PCIe, 1GbE, USB, SPI와 같은 고성능 직렬 인터페이스를 사용하면 BOM(Bill of Materials) 축소와 보드 생산 비용을 절감할 수 있다. 이것은 회로 보드 디자인과 레이아웃을 단순하게 해주고, 여러 가지 연결 방법과 분석 데이터를 내놓을 수 있게 해 준다(그림 4).

▲ 그림 4. 66AK2L06 I/O 연결 옵션

1. USB

USB 인터페이스는 호스트와 여러 주변장치들 사이의 데이터 교환을 지원하는 다목적 케이블 버스이다. 이것은 PC나 TI SitaraTM 프로세서 같은 그래픽 프로세서와 접속할 수 있다. 또한 이 인터페이스는 대용량 저장을 위한 하드 드라이브 포트로도 사용할 수 있다.

66AK2L06 SoC에는 두 개의 양방향 USB 레인이 있다. 각 레인마다 주변장치 모드와 호스트 모드에서 Full/High/Super 속도 모드를 양방향으로 지원한다. 호스트 모드일 때는 저속 모드도 지원한다. 이 컨트롤러는 USB 2.0과 하위 호환된다. USB 인터페이스에 필요한 모든 소프트웨어 드라이버들은 MCSDK[2]를 통해 구할 수 있다.

2. 1GbE

66AK2L06 SoC는 802.3 규격 이더넷 트래픽을 위해 다섯 개 포트(네 개는 외부) 기가비트 이더넷 스위치를 갖고 있다. 4개의 외부 포트는 독립형 SGMII 모듈로, 각각 따로 구성할 수 있다. 66AK2L06 SoC가 Linux? 기반 웹 서버를 구현하면 원격 제어도 가능하다. 웹 서버는 RFSDK에서 사용 가능하며 DFE 서브시스템의 제어 및 작동에 사용할 수 있다.

네트워크 코프로세서(NetCP)는 기가비트 이더넷 스위치 너머에 상주하며 헤더 매칭과 CRC 생성 같은 헤더 프로세싱을 위한 패킷 액셀러레이터(PA)와 암호화 및 해독을 위한 보안 액셀러레이터, 내부 패킷 통신을 위한 패킷 DMA 컨트롤러를 구현한다.

NetCP는 최대 1500kpps까지 처리할 수 있다. 이 PA는 L3 리어셈블리, ACL(Access Control List) 프로세싱, 멀티루트 프로세싱 같은 진입 기능들을 지원하고, 진출 IP 단편화에서는 L2 프레이밍과 L4 체크섬이 지원된다. 보안 액셀러레이터는 IPSEC(IKE, AH, ESP, SRTP), 3GPP 등을 위해 최대 6.4Gbps까지 암호화 및 해독을 지원한다.

그 밖의 기능들로는 TRNG(True Random Number Generation)와 공개 키 액셀러레이터가 있다. NetCP를 구동하는 데 필요한 모든 LLD(Low-Level Drivers)는 MCSDK[2]의 일부인 NetLib 소프트웨어에서 구할 수 있다.

3. PCIe

PCIExpress(PCIe) 모듈은 고속 직렬 인터페이스로, PCB나 백플레인에서 주로 사용되며 다른 PCIe- 규격 디바이스와 신뢰할 수 있는 다목적 연결을 보장한다. 각 레인마다 최대 5.0Gbps까지 원시 비트 레이트로 구동할 수 있다. PCIe 인터페이스에 필요한 모든 소프트웨어 드라이버는 MCSDK를 통해 구할 수 있다. PCIe 인터페이스에 대한 자세한 내용은 참고문헌 [2]를 참조한다.

자동화된 테스트 시스템에 주로 사용되는 PCIe 인터페이스 확장형이 계측용 PCI Express eXtension(PXI Express)이다. PXI와 PXI Express는 PXI 시스템 얼라이언스(PXISA)가 주관하는 산업 표준으로, 표준 PCI/PCIe 인터페이스를 바탕으로 저렴하고 튼튼한 고속 인터페이스를 제공하고 있다.

PCI/ PCIe 인터페이스 외에도, 측정 시스템의 정확한 원격제어를 가능하게 하는 타이밍 및 동기화 기능들이 추가됐다. 66AK2L06 SoC는 PCIe를 지원하며, 버퍼링된 GPIO 신호를 사용하면 PXIe 보드 디자인도 가능하다.

4. SPI

SPI(Serial Peripheral Interconnect) 포트는 동기식 직렬 입출력 포트로, 프로그래머블 길이의 비트 스트림을 시프트인/아웃시킬 수 있다.[2]

SPI 포트의 주요 목적은 SPI ROM과 연결해 부트를 실행하는 데 있다. 66AK2L06 SoC에는 세 개의 SPI 포트가 있는데, 이것은 최대 66MHz 속도로 작동 가능하다. 이 인터페이스에 필요한 모든 드라이버들은 MCSDK의 일부이다.

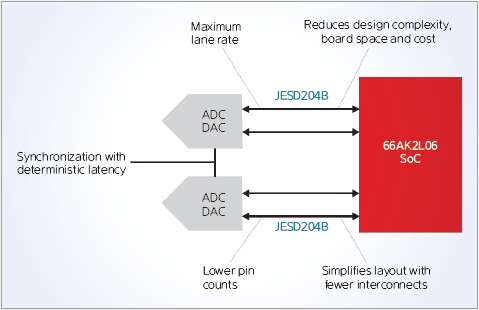

5. JESD204B

JESD204B는 ADC, DAC, DSP, SoC, FPGA, ASIC 사이에서 높은 처리량과 낮은 핀 카운트 직렬 링크를 제공한다. 이 인터페이스는 기존 CMOS나 LVDS 구현에 비해 보드공간과 복잡성이 줄어들었고, 저전력 구현이 가능해졌다. JESD204B의 장점들은 참고문헌 [5]를 참조한다.

66AK2L06 SoC에서 JESD204B 인터페이스는 4개의 양방향 SERDES 레인들로 구성돼 있으며, 이것은 최대 7.3Gbps 레이트로 작동한다. 이것은 DFE 블록과 직접 연결된다. DFE는 이 레인들을 각각 따로 사용하거나 합쳐 사용해 한 개, 두 개, 네 개의 데이터 스트림을 각 방향으로 운반한다. DFE는 데이터 스트림 각각에서 최대 12개까지 디지털 채널들을 분할하거나 집합할 수 있다. 이 인터페이스는 JESD204A와의 하위 호환을 위해 JESD204B 서브클래스 0을 지원하며, 결정론적 레이턴시를 지원하는 서브클래스 1을 지원한다. 그림 5를 참고한다.

▲ 그림 5. JESD 인터페이스의 장점

66AK2L06 SoC 개발 환경

강력한 하드웨어 리소스를 제공하는 것 외에도, 66AK2L06 SoC에 들어 있는 풍부한 개발 툴과 라이브러리로 디자인을 바로 시작할 수 있고 전체 개발 기간을 단축할 수 있으며, 제품 수명기간 내내 업그레이드할 수도 있다. 또한 평가 모듈과 레퍼런스 디자인도 구할 수 있다.

① 66AK2L06 평가 모듈

JESD204B 인터페이스가 FMC 커넥터에 루팅돼 있는 66AK2L06 SoC 평가 모듈. 이 모듈은 TI DAC 및 ADC 평가 모듈과 매끄럽게 연결된다.[6]

② TI 디자인 TIDEP0034

JESD204B 인터페이스를 통해 TI의 ADC12J4000 및 DAC38J84를 66AK2L06 SoC에 연결하고 있는 레퍼런스 디자인. 자세한 내용은 참고문헌 [4]를 참조한다.

③ Code Composer StudioTM

IDE(Integrated Development Environment)는 모든 TI 프로세서 플랫폼을 지원하는 통합 개발 환경으로, 임베디드 애플리케이션을 개발하고 디버깅하는 데 쓰인다. 이것은 C/C++ 컴파일러, 소스코드 편집기, 프로젝트 빌드 환경, 디버거, 프로파일러, 라이브러리 등의 툴들로 구성돼 있다.

④ MCSDK

TI ARM 및 DSP 기반 디바이스를 위한 기반 소프트웨어를 제공한다. 여기에는 다음과 같은 컴포넌트들이 포함돼 있다.

• DSP 코어의 SYS/BIOS 실시간 임베디드 운영시스템

• ARM 프로세서에서 실행되는 리눅스 하이레벨 운영 시스템(멀티코어 ARM 프로세서를 위한 SMP 모드)

• DSP 칩 지원 라이브러리, DSP/ARM 드라이버, 기본 플랫폼 유틸리티

• 코어와 디바이스에서의 인터-프로세서 통신

• SoC 리소스 관리

• 트레이스 디버그와 계측

• 부트로더와 부트 유틸리티, 파워-온 셀프 테스트

• 최신 툴 체인(Linaro, DSP TI CodeGen)

• 호스트 툴, 통합 개발 환경

⑤ DSPLib

이 라이브러리는 Code Composer Studio IDE의 일부로 소스가 제공되며, 여기에는 여러 애플리케이션에서 빌딩 블록으로 사용되는 여러 가지 디지털 신호 처리 기능들의 포트폴리오가 들어 있다. 이 루틴들은 C66x 코어의 모든 기능을 활용해 고도로 최적화되어 있으며, 고정 및 부동소수점 커널이 둘 다 포함돼 있다. DSPLib에는 다음과 같은 기능들이 있다.

• 어댑티브 필터링

• 필터링 상관관계

• FFT(Fast Fourier Transform)

• 필터링과 컨볼루션

• 매트릭스 계산

⑥ RFSDK

66AK2L06 SoC 내부의 DFE 블록, JESD204B 인터페이스, 그리고 JESD 인터페이스에 연결된 모든 ADC, DAC, AFE를 설정 및 제어하는 데 사용되는 일련의 API들이 들어 있다.

⑦ NetLib/TransportNetLib

MCSDK의 일부로 제공되며, ARM 사용자 공간 애플리케이션을 위한 소프트웨어 패키지로 구성되어 있어 NetCP에 대한 접속 권한을 얻을 수 있다. NetLib에는 두 개의 메인 소프트웨어 컴포넌트인 HPLIB(High-Performance Lib)와 NetAPI(Network API) 모듈이 들어 있다. HPLIB는 고속 경로 애플리케이션에 최적화된 낮은 오버헤드 라이브러리이고(사용자 평면, UDP/IP), NetAPI에는 송신/수신 API가 데이터 경로 구성과 함께 들어 있다(제어 평면, GTP/IP).

☆

TI의 KeyStoneⅡ 아키텍처를 기반으로 하는 66AK2L06 SoC는 확장 가능한 저전력 솔루션으로, 통합 FFT 하드웨어 가속과 DFE, 고속 JESD204B 인터페이스, 네트워크 코프로세서, 통합 GBE 스위치 등의 프로세싱 시스템을 갖추고 있다.

이 플랫폼은 FFTC와 C66x DSP 코어를 이용해 최대 46MFFT까지 FFT 성능을 제공하며, SNR의 범위는 84dB(고정소수점)부터 300dB(부동소수점)까지 다양하다. JESD204B 인터페이스는 아날로그 프론트 엔드나 데이터 컨버터와의 고속, 저속 연결을 바로 제공한다.

C66x 코어가 풍부한 신호 처리 소스 코드 라이브러리로 효율적인 신호 처리 능력을 발휘한다면, ARM 코텍스-A15 코어는 리눅스 기반의 방대한 오픈소스 라이브러리와 서비스에 대한 접근성을 제공한다. 이러한 기능들과 풍부한 I/O들 덕분에 SWaP-C, 출시 기간, 미래지향성 등 T&M 시장의 까다로운 요건을 충족시키는 뛰어난 SoC 플랫폼이 되었다.

이 디바이스는 신호생성 및 신호분석을 위한 T&M 애플리케이션 디자이너들에게 다양한 애플리케이션들을 처리할 수 있는 단 하나의 하드웨어 및 소프트웨어 플랫폼을 제공한다.

Magnus von Brömssen, Béatrice Philibert

TEXAS INSTRUMENTS